Sujeten:

- Aféierung

- Logik Gates

- Kombinatoresch Circuiten an Autosapplikatiounen

Aféierung:

D'Informatiounsveraarbechtung vu modernen Gefierer ass gréisstendeels, oder net ganz, digital. Déi digital Informatioun besteet aus elektresche Spannungen, wou e Jo/Nee oder On/Off geformt gëtt op Basis vum Spannungsniveau. An Interface elektronesch läit op engem A/D Konverter (Analog / Digital), wou eng Sensorspannung an eng digital Noriicht ëmgewandelt gëtt, déi aus Eeneren an Nullen besteet.

An der digitaler Elektronik schwätze mir vun engem logeschen 1 oder engem logeschen 0. D'Spannungen sinn um TTL Niveau (Transistor Transistor Logic).

- Jo oder weider: logesch 1: 5 V an

- Nee oder aus: logesch 0: 0 V an

Basis elektronesch Circuiten op ECUs enthalen vill ICs déi Logikkreesser erstellen. Dës logesch Circuiten enthalen logesch Paarte, déi vun der CPU entweder Hardware oder Software kontrolléiert kënne ginn.

Logik Gates:

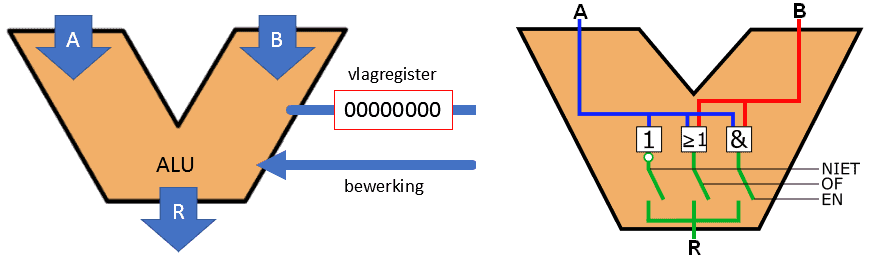

D'ALU (Arithmetic Logic Unit) ass den zentrale Deel vum Mikroprozessor an enger ECU. D'ALU mécht arithmetesch a logesch Operatiounen. D'ALU iwwerpréift och wou an der Erënnerung de nächste Kommando vum Programm ass, deen ausgefouert gëtt.

D'ALU enthält logesch Paarte, déi dacks aus Silizium Hallefleit opgebaut ginn. D'Logik Paarte kënnen Operatiounen bannent e puer Nanosekonnen mat engem binäre Code ausféieren; eng Kombinatioun vun eent an Nullen. Dëst gëtt e Kommando deen aus zwou Méiglechkeeten besteet: op oder aus, konduktiv oder net konduktiv. Multiple Kommandoe ginn gläichzäiteg an der ALU veraarbecht a schaffen zesummen fir e "Wuert" mat 8, 16 oder 32 Bits ze bilden, laut der Computerarchitektur. E Wuert ass déi gréisste Quantitéit un Daten, déi an engem eenzegen Dateregister gespäichert sinn. Dëst ass d'Quantitéit vun Donnéeën, déi vum Prozessor op eemol veraarbecht kënne ginn.

Déi folgend Basisoperatioune fënnt an enger ALU statt:

- eng oder méi Bitpositiounen no lénks oder riets bewegen (verréckelen)

- arithmetesch Operatiounen op zwee Wierder ausféieren, wéi Zousatz oder Zousatz (addéieren);

- logesch Operatiounen op d'Donnéeën ausféieren (AN, ODER, NET, NAND, NOR, XOR, XNOR).

D'Biller hei drënner weisen d'ALU als Symbol (lénks) a mat den IEC Symboler, déi d'Operatioun vun A a B (akommen) op R (ausgaende) iwwersetzen.

D'NET, ODER an AN Paarte, déi mir am richtege ALU gesinn, sinn déi heefegst Paarte fir logesch Operatiounen auszeféieren. Et gi Häfen déi zousätzlech zu dësen dräi Basishäfen sinn. Mir komme méi spéit op dëser Säit zréck. Mat den NET, ODER an AN Paarte kënnen d'Resultater vun den Input virprogramméiert ginn. Mat Hëllef vun engem Circuit, deen eng Äntwert wéi Jo/Nee oder Wourecht/falsch op zum Beispill d'Handbrems-Warnlicht setzt, kann d'Liicht op zwou Inputen aktivéiert ginn.

- ass d'Handbrems ugewannt?

- ass den Niveau vum Bremsflëssegkeetsbehälter richteg?

Wann eng oder zwou Äntwerte mat "Jo" geäntwert kënne ginn, gëtt d'Warnlicht ageschalt. Méi Beispiller kommen weider op dëser Säit.

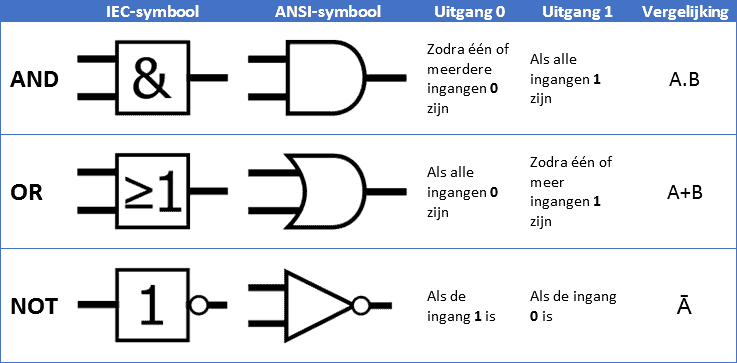

Den Dësch hei drënner weist dës dräi Basis Häfen. Op dëser Säit benotze mir haaptsächlech déi englesch Nimm (AND amplaz EN) fir Iech als Lieser keng Duercherneen ze kreéieren, awer béid sinn natierlech richteg. Dat selwecht gëllt fir d'Symboler (IEC an ANSI). Mir applizéieren d'IEC Symboler, awer an der amerikanescher Literatur gesi mir haaptsächlech d'ANSI Symboler. Déi folgend gëlt och: net vermëschen an eng Zort Symbol benotzen.

Ënnert der Tabell gëtt eng Erklärung iwwer d'Eegeschafte vun all Paart ginn an d'Wahrheetstabell weist wéi eng Inputen Iech en Ausgang vun 0 oder 1 ginn.

Drënner ass d'Erklärung vun den dräi Paarte mam Symbol an der Wourechtstabell, déi d'Ausgänge fir verschidden Inputkombinatiounen weisen.

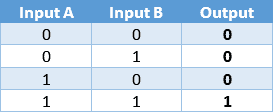

AN Gate:

Den AND Gate (Hollännesch: AND Gate) kann e puer Inputen hunn, awer huet ëmmer nëmmen een Ausgang. Am Bild gesi mir d'Inputen a a b. Et ass méiglech en 1 oder en 0 op béid Inputen ze setzen, onofhängeg vuneneen. Den Ausgang (Q) gëtt 1 wann béid Input (a a b) 1 sinn. An all anere Fäll ass den Ausgang Q 0.

- Mat zwee Inputen vum AND Gate (an dësem Fall Input A a B), ginn et véier méiglech Circuiten fir en Ausgang ze generéieren. Dës ginn an der Wourecht Tabell gewisen, riets vum AND Gate Bild.

- Mat véier Input ginn et 16 Méiglechkeeten;

- Mat aacht Input ginn et souguer 256 Méiglechkeeten.

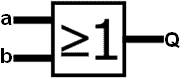

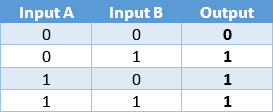

ODER Gate:

Den ODER Gate (Hollännesch: OF Gate) kann och e puer Inputen hunn, mat engem Ausgang. Mat engem ODER-Paart ass den Ausgang 1 wann ee vun deenen zwee Input en 1 ass, oder wa béid Input en 1 sinn.

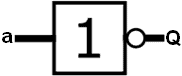

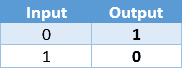

NET Gate:

Den NOT Gate (Hollännesch: NOT Gate) funktionnéiert als Inverter an huet nëmmen een Input an Output. D'Input Signal gëtt ëmgedréint: wann den Input Signal 1 ass, gëtt d'Ausgangssignal 0 a vice versa.

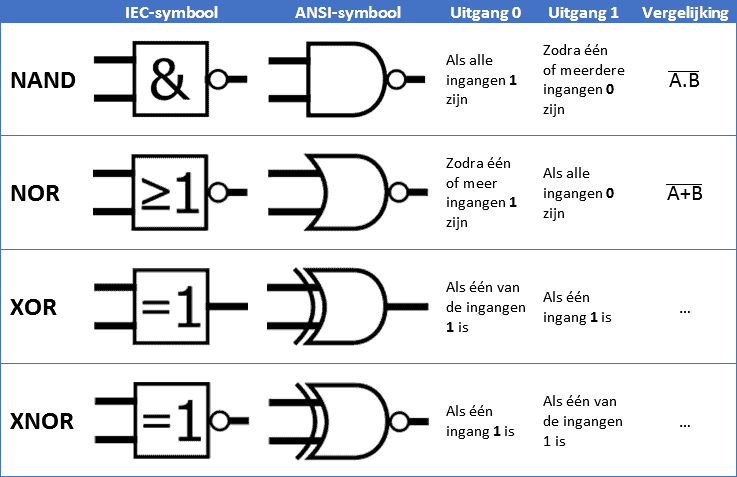

Nieft de Circuiten ernimmt (AN, ODER an NET), mir wëssen och eng Rei vun derivéiert Logik Kreesleef. Mat dëse Circuiten kënne mir zwee vun de virdru diskutéierte Circuiten an ee Circuit kombinéieren.

NAND Gate:

Den Net-AN Paart ass en AN Paart gefollegt vun engem NET Paart. Den Ausgang ass 1 wann verschidde Inputen en 1 hunn. Nëmme wann all Input en 1 hunn, ass den Ausgang en 0. Dëst ass genau de Géigendeel vum AND-Paart, deen virdru diskutéiert gouf.

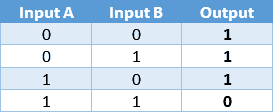

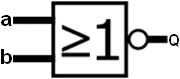

NOR Gate:

Den Net-ODER Paart (Net-ODER Paart) ass en ODER Paart gefollegt vun engem NET Paart. Et kann e puer Inputen hunn an huet nëmmen een Ausgang. An dësem Circuit ass den Ausgang nëmmen 1 wann béid Inputen 0 sinn.

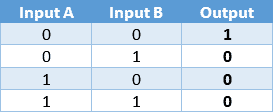

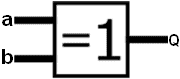

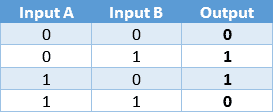

XOR Gate:

Den eXclusive-OR Gate ass e Paart deem säin Ausgang 1 ass wann nëmmen een Input 1 ass. Wann béid Inputen deeselwechte Logikzoustand hunn, gëtt den Ausgang en 0. D'XOR Gate huet ni méi wéi zwee Input.

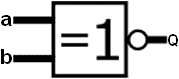

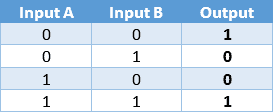

XNOR port:

Den eXclusive-ODER Paart ass mat engem NET Paart ausgestatt, wat et en eXclusive-NOT-ODER Paart mécht. Den Ausgang gëtt um XOR Paart ëmgedréint.

Fir all IC ass et wichteg datt souwuel eng Energieversuergung wéi och den Terrain verbonne sinn fir e zouenen Circuit z'erreechen. Béid Häfen mussen och eng Spannung kréien fir eng schwiewend Messung ze vermeiden. Pull-up an Pull-Down Resistors sinn erfuerderlech fir d'Inputen an d'Ausgänge richteg ze wiesselen. Ouni dës Widderstänn kënnen d'Ports "aktiv" bleiwen wann se net kontrolléiert ginn. D'Ports sinn dann net zouverlässeg.

Kombinatoresch Circuiten an Autosapplikatiounen:

Déi digital ICs kënne matenee verbonne ginn andeems Dir den Ausgang vun engem IC un den Input vun deem aneren IC verbënnt. Mat dëse Kombinatioune kënne Circuiten gemaach ginn, déi eng gewënscht Ausgangskombinatioun fir all gewënschten Inputkombinatioun produzéieren. Wann verschidde ICs matenee verbonne sinn, nenne mir dëst e Kombinatiounskrees. Fir e Gefill fir d'Kombinatiounskreesser ze kréien, ginn automobiltechnesch Beispiller hei ënnen uginn.

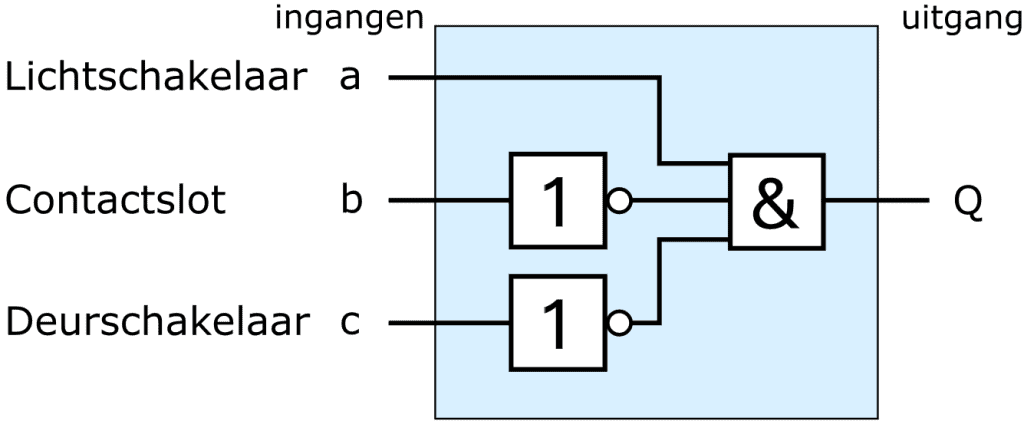

Liicht Warnung Circuit:

E praktescht Beispill vun engem Kombinatiounskrees ass dat vun der Luuchtwarnung. Wann d'Zündung ausgeschalt ass an d'Dier opgemaach gëtt, während d'Bauluuchten op sinn, muss de Chauffeur vun engem Buzzer gewarnt ginn. Den AND Gate gëtt fir déi dräi Input Signaler benotzt. Wéi an der viregter Sektioun beschriwwen, mussen all Inputen zum AND-Paart 1 sinn fir en 1 op der Ausgang ze kréien an de Buzzer ze aktivéieren. Wann ee vun den dräi Inputen zum AND-Paart en 0 ass, bleift den Ausgang 0 an de Buzzer bleift ausgeschalt.

- Liichtschalter: wann de Schalter ausgeschalt ass, weist den Input a en 0. Wann d'Parkplazen oder d'Déifstrahlliichter ageschalt sinn, gëtt dëst eng 1;

- Zündslot: wann d'Zündungsschloss ageschalt ass, erschéngt eng 1 um Input b. Wann d'Zündung ausgeschalt ass, en 0. An dësem Fall dréit d'NET-Paart den 0 an en 1 ëm, fir dat richtegt Signal fir den AND-Paart ze kréien.

- Dierschalter: wann eng Dier op ass, gëtt d'Signal op de Buedem gewiesselt. Just wéi mam Zündschalter, muss den 0 op en 1 ëmgedréit ginn fir datt den AND-Paart richteg funktionnéiert.